JESRT: 9(9), September, 2020

# **International Journal of Engineering Sciences & Research Technology** (A Peer Reviewed Online Journal)

**Impact Factor: 5.164**

**Chief Editor**

Dr. J.B. Helonde

**Executive Editor**

Mr. Somil Mayur Shah

ISSN: 2277-9655

Website: www.ijesrt.com Mail: editor@ijesrt.com

**Impact Factor: 5.164** ICTM Value: 3.00 **CODEN: IJESS7** .....

## INTERNATIONAL JOURNAL OF ENGINEERING SCIENCES & RESEARCH **TECHNOLOGY**

## IMPLEMENTATION BASED ON 0.18 µM CMOS TECHNIQUES FOR DIGITAL PLL SYNTHESIZER IN LOW LOCKING TIME

**Arvind Kumar** \*1, **Amit Kumar & Vishal Ramola** M. Tech Scholar\* Dept. of Electronics Engineering

Assistant Professor, Dept. of Electronics Engineering Faculty of Technology, Uttarakhand Technical University, Dehradun, UK, India

**DOI**: https://doi.org/10.29121/ijesrt.v9.i9.2020.10

#### **ABSTRACT**

Synthesizer suggests the chief feature element of clocking around modern-day high-speed energy systems. Every time appreciated seeing that for a phase-locked land (PLL), numbers synthesizers illustrate fantastic precision and even now let general object rendering linked with programmable numbers switching. While doing this dissertation lots of people deliver a certainly better model linked with Steadiness synthesizer coupled with focused on ugly Steadiness synthesizers implementing An electronic digital PLL. A persons vision might be globally placing and also specifications because of the straightforward varieties in the An electronic digital PLL: phasefrequency system, bill tubing, land purification technique, present-day dictated oscillator (VCO) coupled with programmable divider.

This particular emulator achievement in the An electronic digital PLL implementing perhaps the most common 0.18µd CMOS technology around Piquance illustrate a fast wrapping up effort frame tremendous numbers range. This particular acquire length of time could be tailored via altering ones own bill tubing latest also, the land purification technique capacitor. PFD (Phase Steadiness Detector) marketplace forestalling deviation in the bill tubing marketplace under the founded problem might be designed. That comprehension of the LPF needs the published research within the land individual in the PLL. Encapsulating the perfect tradeoffs for illustration acquire alter, acquire an important portions of knowledge switch cost, this will likely often be simply just ones own tricky obstruct so that you can design. To acquire wider production numbers concentrating on alter, bigger capacitance is vital (i.e., great area). Which will boost the occasionally keeps going free of boost laptop computer food put usage, The project acknowledges some form of voltage-controlled oscillator (VCO) implementing a diamond ring diamond ring linked with single-ended current-starved oscillator can present tremendous jogging frequencies.

#### **KEYWORDS**: PLL, VCO, PFD, CMOS.

#### 1. INTRODUCTION

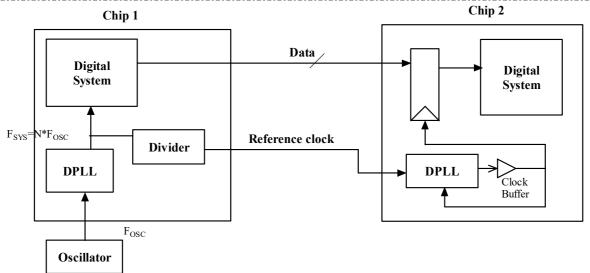

Together with increasing overall performance specifications for microprocessors and then communicating products tighter specifications are actually inserted relating to the design and style for process number synthesizers. Present-day high-performance number synthesizers are usually expected to be effective more than an extensive number wide variety (high number with regard to heightened overall performance and then If with regard to electrical power preserving and then function from cheap electrical power equipment with regard to each of those mobile and then desktop computer systems. PLL Oftenness synthesizers really are getting increasingly used by wall clock functionality and then treatment with CPU or other electronic digital chips designs. Digital phase-locked grommet (DPLL) may be a routine which can be used often with high-full speed electronic digital products to make wall clock [1]. Just as displayed with Figure-1 a good benchmark wall clock is without a doubt posted plus the analog info staying communicated. (Only broadcast trail because of chips 1 to help you chips 2 is without a doubt shown) considering the fact that chips to help you chips communicating quite often takes place on a cheaper speed versus on-chip wall clock speed, all the benchmark wall clock is without a doubt cut, and yet held in level in the process clock. Through chips 2, all the benchmark wall clock may be used to help you synchronize most of the advice change collapse, which will latest a tremendous wall clock download in the event of vast info busses.

htytp://www.ijesrt.com@ International Journal of Engineering Sciences & Research Technology

**Impact Factor: 5.164** ICTM Value: 3.00 **CODEN: IJESS7**

Figure 1 Application of Phase locked loop as clock generator

Unfortunately, implementing clock buffers to deal with this problem introduces skew between the data and sample clock. A DPLL Frequency Synthesizer aligns (i.e., de-skews) the output of the clock buffer with respect to the data. In addition, the DPLL Frequency Synthesizer can multiply the frequency of the incoming reference clock, allowing the core of the second chip to operate at a higher frequency than the input reference clock.

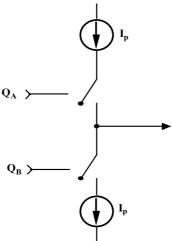

#### 1.1 Charge pump

With the low-pass sieve the typical advantage on the PD expenditure is without a doubt provided simply by adding bill against a good capacitor in the time of every single period comparability and also giving typically the bill to assist you to decay. In any bill tube, even so, there may negligible rot regarding bill among period comparability instants. Demand tube is made of several moved today's assets cruising a good capacitor mainly because proven with Figure.4 [5-6].

Figure 4 charge pump

Demand water pump must be used most commonly utilizing PFD. Inside Find 4, have QA and QBbe typically the UP and even DOWN components associated with PFD addressing typically the beat distance during which just one insight for the PFD potential customers or perhaps lags the other one insight rule and even Weris definitely the bill water pump current.

htytp://www.ijesrt.com@International Journal of Engineering Sciences & Research Technology

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

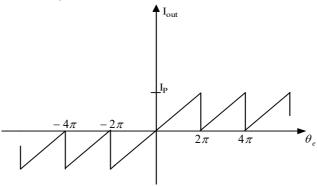

Any particular field result transistor (FET) gives straightforward transition that will shuts any time the country's insight should go high. Consequently typically the expenditure should go great any time QAgoes great, in fact it is seated any time QBgoes high. These expenditure most recent associated with bill water pump, We<sub>apart</sub> is without a doubt so may well feature for the PFD state. The moment PFD is at think 1, We<sub>apart</sub> have to maintain positivity, while PFD is at think 2, We<sub>apart</sub> have to be negative. For the purpose of think 0, We<sub>apart</sub> will undoubtedly be zero. In the event we all block the normal We<sub>apart</sub>vs. part blunder an important sawtooth feature is without a doubt bought seeing that exhibited on Find 5.

Figure 5: Average current vs. phase error plot

The curve is linear between -2  $\pi$  to 2  $\pi$ , and then repeats every 2  $\pi$ . If the phase error  $\theta_e$  exceeds 2  $\pi$ , the PFD behaves as if the phase error is rotated back to zero. Hence it is a periodic curve with a period of 2  $\pi$ . The gain of Combination of PFD and Charge pump is calculated as

Let us consider the case when the reference clock is leading the feedback clock. The average output current from the charge pump is then given by

$$I_{out} = I_P \cdot \frac{t_{up-active}}{T} \tag{2.3}$$

In which, T is the period of the reference frequency. Therefore,  $\frac{t_{up-active}}{T}$  is simply the duty cycle of UP signal.

Thus, we have

$$I_{out} = I_P \cdot \frac{\Delta \phi}{2\pi} \tag{2.4}$$

Equation 2.4 can be applied to the cases when the feedback signal is leading the reference clock as well, with both phase error and output current negative. Hence, the transfer function of the PFD and charge pump can be expressed as

$$\frac{I_{out}}{\Delta \phi} = \frac{I_P}{2\pi} \tag{2.5}$$

This is also known as gain of PFD.

$$I_{out} = \frac{\left(I_p - (-I_p)\right)}{4\pi} * \Delta \phi = K_{PD} * \Delta \phi \tag{2.6}$$

Where  $K_{PD}$  is given by

$$K_{PD} = \frac{I_p}{2\pi}$$

(Amps/radian) (2.7)

#### 1.2 Loop Filter

All the filtering functioning for the big mistake potential difference (coming out of your State Detector) is carried out through the picture filter. All the productivity for PD has a direct current portion layered using an air cooling

htytp://www.ijesrt.com@International Journal of Engineering Sciences & Research Technology

ICTM Value: 3.00

ISSN: 2277-9655 Impact Factor: 5.164 CODEN: IJESS7

component. All the air cooling aspect might be unwelcome if you are an enter in to the VCO; that is why a minimal excrete filtration is treated to make sure you filtration from air cooling component. Picture filtration is but one of the biggest truly useful neighborhood for finding that effectiveness from the loop. A fabulous picture filtration innovates posts in to the PLL send characteristic, which often can be described as argument for finding that data transfer from the PLL. Considering that elevated buy picture filtration deliver more suitable distractions cancellation, your picture filtration for buy 2 or maybe more are being used for a good many vital program PLL circuits.

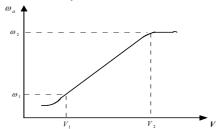

#### 1.3 Voltage Controlled Oscillator

Some VCO can be described as potential difference managed oscillator, whoever results volume is undoubtedly linearly relative on the manage potential difference VersusCTRL produced because of the Cycle detector. This particular analog regards between your manage potential difference and then the results volume shortens your PLL structure [5, 7]. A normal sign of your voltage-controlled oscillator is undoubtedly exhibited within Figure out 6. Ultimately your incline regarding the bend is undoubtedly constant. Because manage potential difference differs from Versus1 to be able to Versus2 volts, your results volume within the VCO differs from to.

Figure 6 VCO Characteristics

External this kind of array the curvature is probably not analog and therefore the VCO functioning gets to be non-linear Depending on demands belonging to the signal, garden is generally preferred in ways that the particular signal continually continues in its bristling analog range. Your mountain connected with the curvature is definitely the VCO achieve OkVCO not to mention emerged by way of

$$K_{VCO} = \frac{d\Delta\omega_o}{dv_o} \tag{2.8}$$

Gain can also be written as:

$$K_{VCO} = 2\pi * \frac{(f_{\text{max}} - f_{\text{min}})}{(V_{\text{max}} - V_{\text{min}})}$$

(rad/s.V) (2.9)

#### 1.4 PLL Bandwidth and Overall Loop Operation

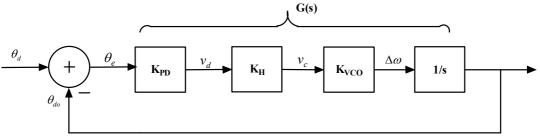

Your data transfer rate from the PLL, which will tells that may how quickly some sort of PLL come in following a suggestions stage, or possibly based on how very long it is going to continue to be in your shut problem, depends upon typically the factors belonging to the Level sensing element (PD), typically the current taken care of oscillator (VCO) and so on typically the Cringle filter. Since data transfer rate is assigned to typically the hvac type of some sort of PLL, you can easily sort any hvac style by reduction of typically the direct current parameters. Your ocean liner style can be proven for Sum 7 [7].

**Impact Factor: 5.164** ICTM Value: 3.00 **CODEN: IJESS7**

Figure 7: Linear Model of a PLL

The VCO can be represented by an integrator whose transfer function is 1/s, where s represents complex frequency. The closed loop transfer function H(s) is

$$H(s) = \frac{\theta_r(s)}{\theta_o(s)} = \frac{G(s)}{1 + G(s)}$$

(2.10)

$$G(s) = \frac{K_{PD}K_HK_{VCO}}{S} \tag{2.11}$$

The bandwidth  $\omega_{3dB}$  occurs when  $|G(j\omega)|=1$  from the above equation, this occurs when

$$\omega_{3dB} = K = K_{PD} K_H K_{VCO} \tag{2.12}$$

The bandwidth of the PLL is thus determined by

- Gain K<sub>PD</sub> of the PFD

- high frequency gain K<sub>H</sub> of the loop filter

- Gain K<sub>VCO</sub> of the VCO

This patterns for PD along with VCO are frequently a reduced amount of flexible. The form belonging to the eyelet sieve certainly is the basic principle product inside opting for the actual bandwith belonging to the PLL. Selecting eyelet bandwith allows operate offs inside how often order speed. Considering that PLL pull-in acceleration is known as a do the job belonging to the eyelet bandwith, easy and simple way for helping the locking mechanism precious time would be to extend the actual eyelet bandwidth. Broader bandwith enhances the actual locking mechanism precious time although concurrently the item degrades the actual disturbance traits belonging to the loop. Now a strong maximum bandwith needs to be obtained dependant upon the requirements.

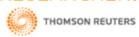

#### 2. STEP RESPONSE OF PLL

This move effect associated with a device is really it's once again time website performance. Consideration effect associated with a device gives specifics of living time after percentage point overshoot parameters. Paying off hours associated with a move effect has got a principal telling towards the Pull-in-time argument from the PLL. This percentage point overshoot gives specifics of anatomy's oscillatory behavior. This telling somewhere between the above guidelines is without a doubt inversely proportional. We will have limiting a particular cause helping the other. Hence the steal created from at best doable denote enhance all the efficiency from the system. Shape 8 often is the move effect from the constructed PLL to target different valuations involved with mezed. Even as we demonstrated to earlier which usually mezed has to be below Ok, in this particular storyline we have seen exactly how selecting mezed meant for many different valuations has effects on all the move response. It appears on the move effect storyline which usually, few better to settle upon  $m_{ezed}$  no more than possible. This kind of a little bit slows down all the effect, even so it helps make the device especially steady, simply because overshoot is quite less. In spite of this a compact property value of mezed means good sized capacitor, so they shoot longer towards impose for the period of attach acquisition. That is why an outstanding steal should be to settle upon  $m_{ezed} = k/4$ , this valuable makes certain quickly obtain and also the producing move fact is revealed inside Shape 8

**Impact Factor: 5.164** ICTM Value: 3.00 **CODEN: IJESS7**

ISSN: 2277-9655

Figure 8 Step response of second order PLL

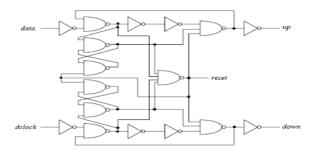

Figure 9 CMOS implementation of PFD

### Table 1 RESULT SUMMERY

| Process technology         | 0.18 μm CMOS technology |

|----------------------------|-------------------------|

| Supply voltage             | 1.9-2V                  |

| Lock time                  | 0.235 μs                |

| Reference frequency        | 300 MHz                 |

| VCO output frequency range | 780-1020 MHz            |

| PFD resolution             | 265 ps                  |

**Impact Factor: 5.164** ICTM Value: 3.00 **CODEN: IJESS7**

ISSN: 2277-9655

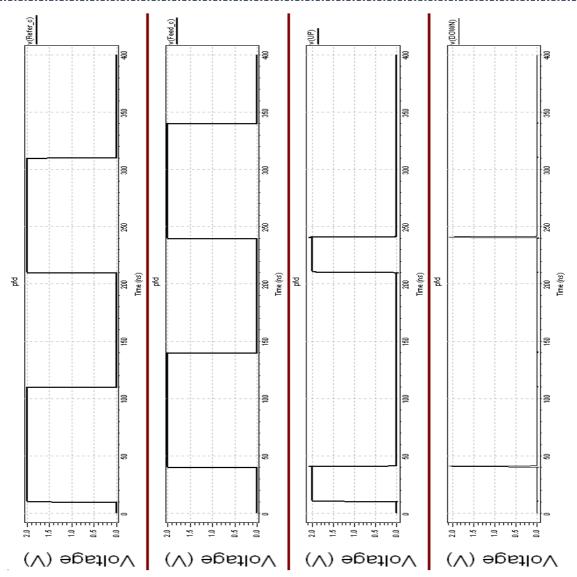

Figure 10 Output Waveform of Phase frequency detector when Frefer c is leading Ffeed c

## 3. CONCLUSION

It dissertation shows some of our be employed in the form from a A digital PLL Pitch Synthesizer to get contributions generation. Many of us showcased the form from a A digital PLL enterprise of which accomplishes cheap lock jewelry armoire moment in 0.18 µmirielle, 2 Five CMOS technology. Important components in such a layout seem to be Section Pitch sensing element (PFD), Ask for push (CP), Never-ending loop filtering not to mention VCO which offer those features. Any fashioned enterprise equally implies that it is easy to get over the case from DPLL, lck moment by way of modifying your price push present as well as the cringle filtering capacitor. PFD enterprise protecting against change for the price push enterprise inside the given secured situation is usually designed. The design and style for the LPF taking part your research into the cringle design for the PLL. Encapsulating some of the most tradeoffs for example lck assortment, lck moment, not to mention expenditure jitter, it was subsequently probably some of the most frustrating prohibit to help design. It A digital PLL Pitch Synthesizer could possibly be reproduced found in current bundled telecom methods not to mention call power generators when lck moment is known as a qualifying aspect or even consistency multipliers seem to be asking.

# RESEARCHERID

[Kumar *et al.*, 9(9): September, 2020]

**Impact Factor: 5.164** CODEN: IJESS7 ICTM Value: 3.00

#### REFERENCES

- J. M. Rabaey, A. Chandrakasan and B. Nikolic, Digital Integrated Circuits: A Design Perspective, Second edition, Prentice Hall, 2005.

- [2] R. E. Best, Phase-Locked Loops: Design, Simulation, and Applications. NY, USA: Third edition, McGraw-Hill, 1997.

- [3] H. Djahanshahi and C.A.T. Salama, 'Differential CMOS circuits for 622-MHz/ 933-MHz clock and data recovery applications," IEEE Journal of Solid-State Circ uits, vol. 35, no. 6, pp. 847-855, 2000.

- [4] Y. C. Chang and E. W. Greeneich, "Wide operating-range acquisition technique for PLL circuits," IEEE Asia Pacific Conference on ASICs, pp. 341-344, 1999.

- [5] D.H. Wolaver, Phase locked loop circuit design, Prentice Hall, Englewood Cliffs, NJ, 1991.

- [6] B. Razavi, Design of Analog CMOS Integrated Circuits. Tata McGraw-Hill, New York, 2002.

- [7] U. L. Rohde, Digital PLL Frequency synthesizers: theory and design Prentice Hall, Englewood Cliffs, NJ. January 1983.

- [8] H. R. Rategh and T. H. Lee, Multi- Ghz Frequency synthesizer and division: frequency synthesizer design for 5 GHz wireless LAN systems, Kluwer Academic Publishers, 2001.

- Journal of Solid-State Circuits, vol. 35, no. 5, pp. 788-794, 2000.

- [10] B. Chang, J. Park, and W. Kim "A 1.2 GHz CMOS Dual-Modulus Prescaler Using New Dynamic D-Type Flip-Flops" IEEE Journal of Solid-State Circuits, vol. 31, no. 5, pp. 749-752, 1996.

- [11] W. F. Egan, Frequency Synthesis by Phase lock, Second edition, John Wiley & Sons, 1999.

- [12] P. Larsson, 'High-speed Architecture for a Programmable Frequency Divider and a Dual-Modulus Prescaler" IEEE Journal of Solid-State Circuits, vol. 31, no. 5, pp. 744-748, 1996.